About me

I am a second-year Ph.D. student at Arizona State University, where I am fortunate to be advised by Prof. Vidya A Chhabria. Currently, my research is centered around sustainable computing and chiplet-based heterogeneous integration architecture. I also actively work with Prof. Aman Arora.

I received my Bachelor’s in Electronics and Telecommunication Engineering from R.V. College of Engineering, I then graduated with a Master’s in Electrical Engineering from Arizona State University.

I have a strong interest in fitness, and in my leisure time, I engage in long-distance running.

Recent News

- [Jun, 2025]. Our dataset work CarbonSet containing 1600+ desktop and datacenter CPUs/GPUs covering design, performance, and sustainaiblity metrics is open sourced! Check it out CarbonSet GitHub

- [Apr, 2025]. Our paper CarbonSet paper is accepted by GVLSI 2025!

- [Nov, 2024]. Invited to give a short talk titled "Extending ACT to evaluate HI and FPGA for Sustainable Computing" at ACT Tutorial at MICRO 2024

- [Nov, 2024]. Will be attending IGSCC 2024 co-located with MICRO 2024 at Austin to present our work "Beyond the Surface: The necessity for Detailed Metrics in Corporate Sutainaiblity Reports"

- [Oct, 2024]. Our paper titled "Beyond the Surface: The necessity for Detailed Metrics in Corporate Sutainaiblity Reports" is accepted at IGSCC 2024!

- [July, 2024]. Gave a talk on Sustainable computing work - GreenFPGA and ECO-CHIP Github at Microsoft Research

- [Jun, 2024] Our work on evaluting FPGA as environmentally sustainable computing solution is open-sourced! Check it out GreenFPGA GitHub

- [Jun, 2024]. Attended DAC 2024! at San Francisco, presented my work GreenFPGA paper

- [Mar, 2024]. Attended HPCA 2024! at Edinburgh, Scotland and presented my work ECO-CHIP paper

- [Feb, 2024]. Passed my Ph.D. qualifier exam. Yaay!!

- [Feb, 2024]. Our paper GreenFPGA paper is accepted by DAC 2024!

- [Oct, 2023]. Our work on estimating carbon footprint for heterogeneous chiplet-based systems is open-sourced! Check it out. ECO-CHIP Github

- [Oct, 2023]. Our paper ECO-CHIP paper is accepted by HPCA 2024!

- [July, 2023]. Secured DAC 2023 Young Fellow

- [July, 2023]. Attended DAC 2023 at San Francisco

- [Jan, 2023]. Started my Ph.D. journey!

- Sustainable Computing

- Heterogeneous Integration

- Chiplets

- Computer Architecture

Featured Publications

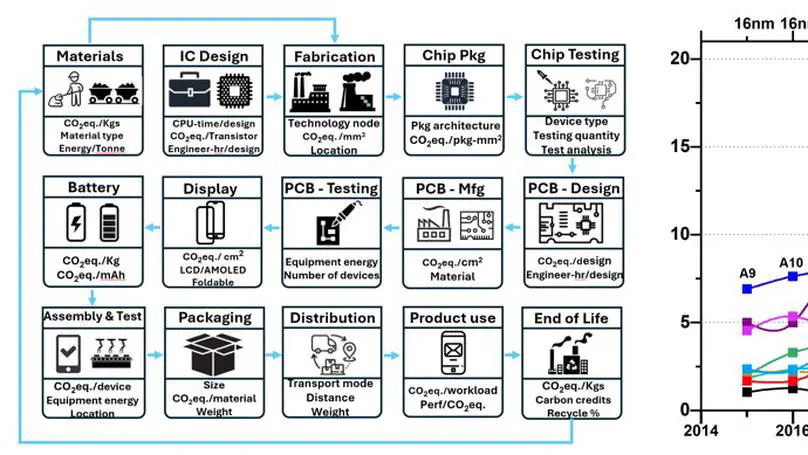

The smartphone industry’s push for smaller, energy-efficient devices with advanced features often overlooks environmental impacts. Corporate sustainability reports provide broad overviews, masking critical details, especially about carbon footprints (CFP) of components like processors. This paper examines the gap between reported CFP trends and the rising CFP contributions of processors, highlighting deficiencies in reporting practices. We propose specific metrics to improve transparency and guide chip design and manufacturing toward sustainable solutions.

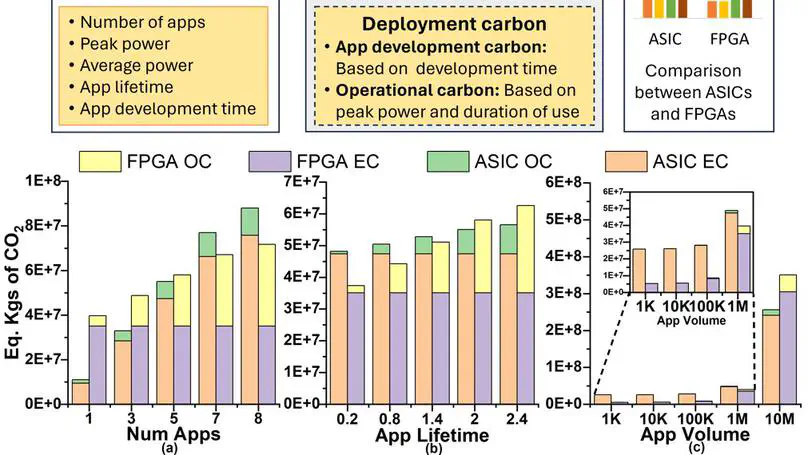

Tool to evaluate the carbon footprint of FPGA-based computing across its lifetime. The tool can also perform comparisons with ASIC counterpart considering differnt aspects such as manufacturing, recycling, disposal, reconfigurability (reuse), operation and design. The sustainable benifits of FPGA compared to ASIC is shown in this work.

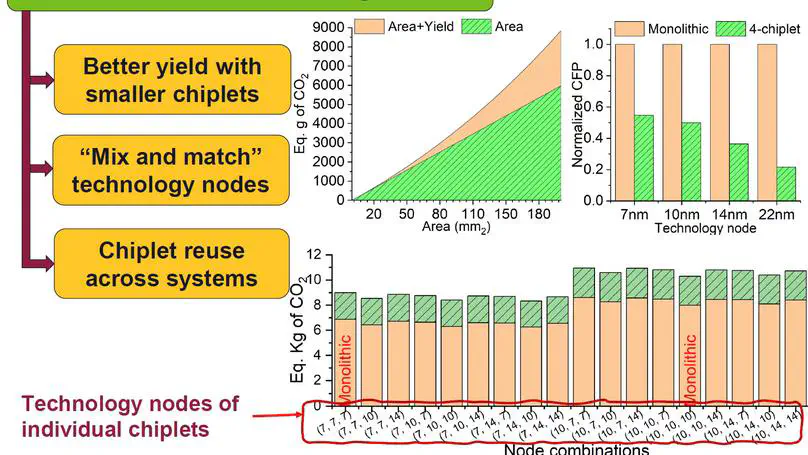

Carbon footprint estimator for heterogenous chiplet-based systems. ECO-CHIP is an analysis tool that analyzes the operational and embodied CFP (design, manufacturing, and packaging). The tool supports the following HI and packaging architectures- RDL fanout, silicon bridge-based, passive and active interposer, and 3D integration. The tool evaluates the crucial package/assembly carbon emissions essential for HI systems, considering size, yield, and assembly process. In addition, it also estimates design CFP.