## **ECO-CHIP: Estimation of Carbon Footprint of Chiplet-based Architectures for Sustainable VLSI**

Chetan Choppali Sudarshan<sup>1</sup>, Nikhil Matkar<sup>1</sup>, Sarma Vrudhula<sup>1</sup>, Sachin S. Sapatnekar<sup>2</sup>, Vidya A. Chhabria<sup>1</sup> Arizona State University<sup>1</sup>, University of Minnesota<sup>2</sup>

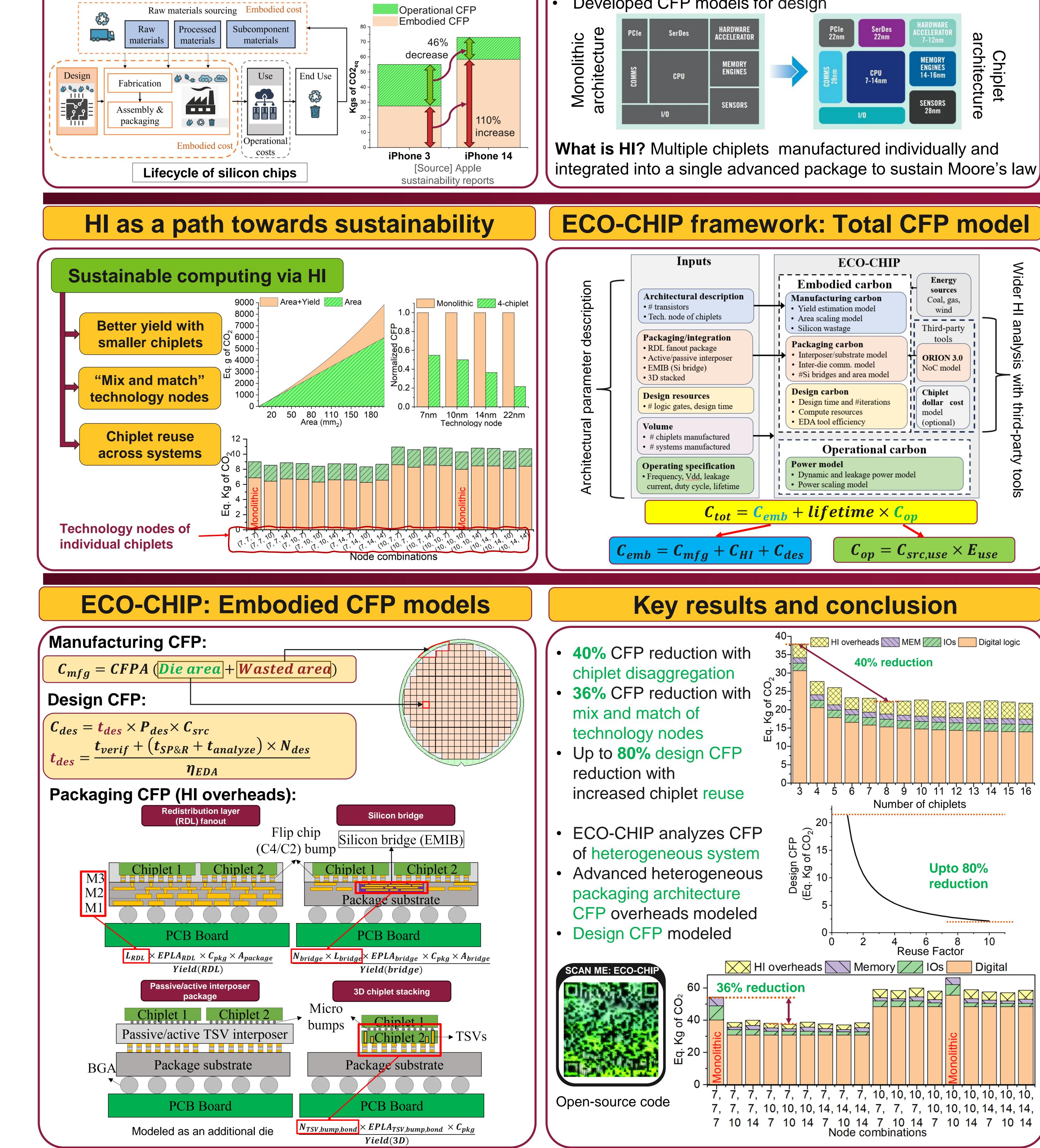

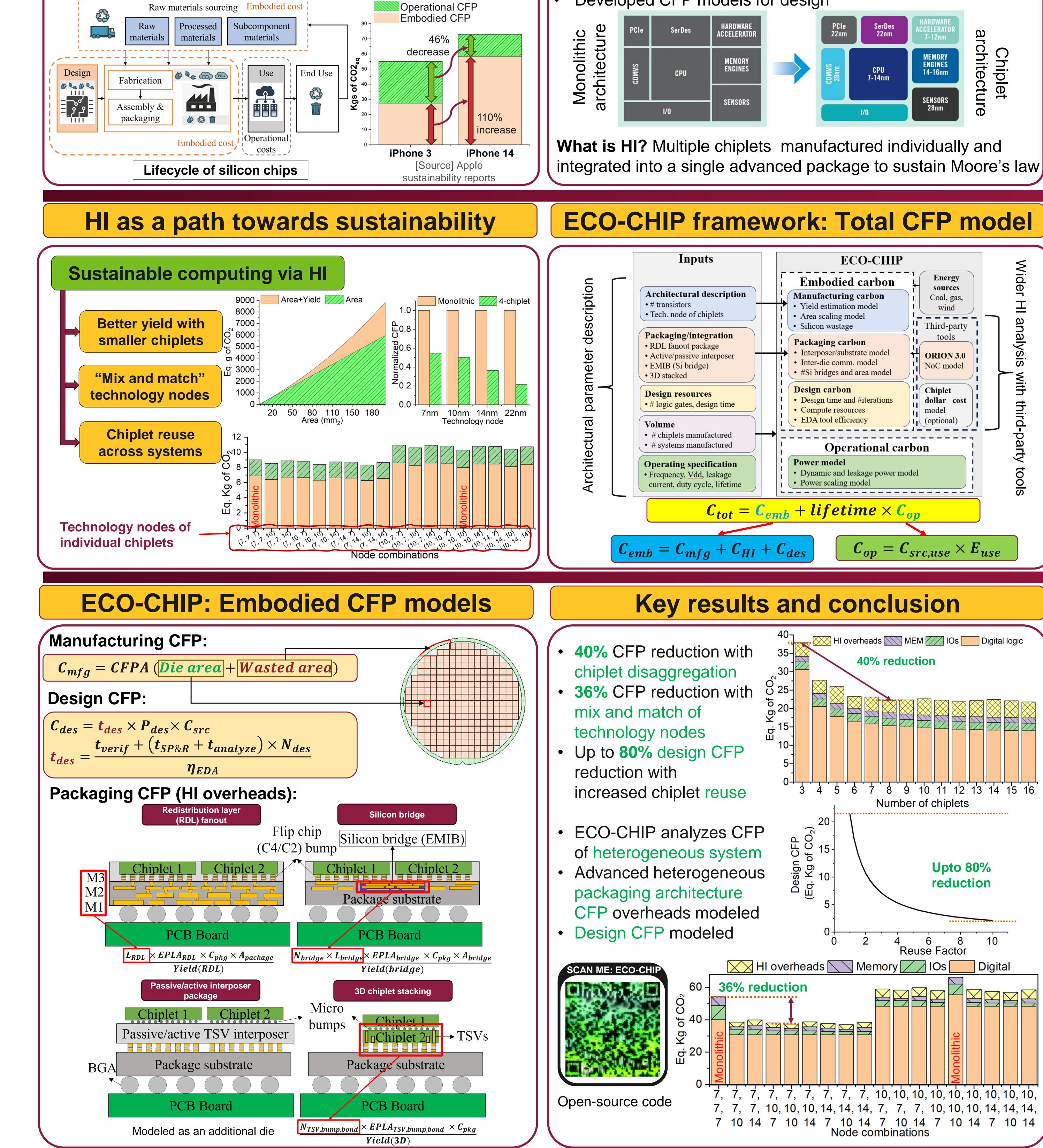

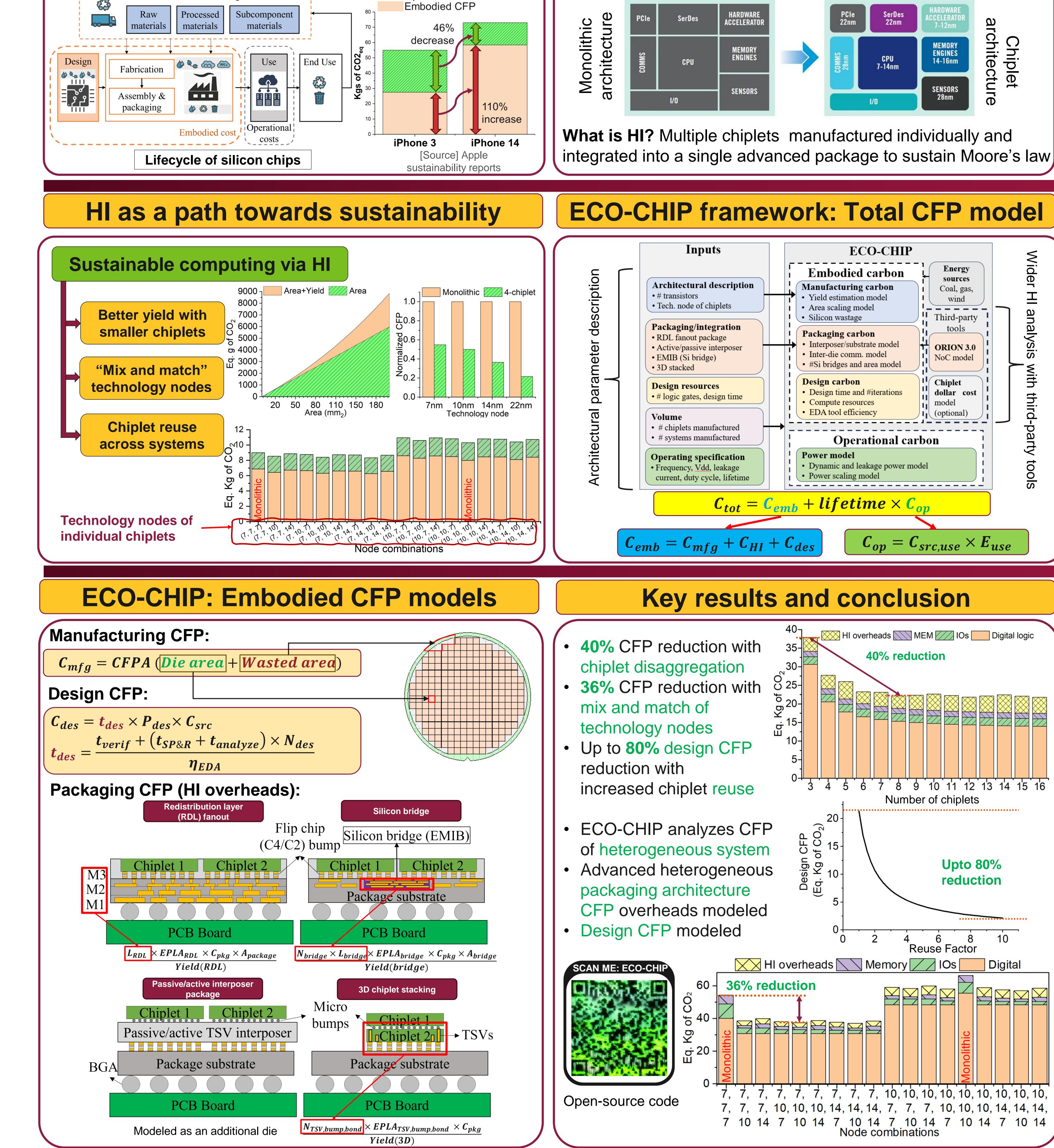

## Introduction and background

- The information and computing technology (ICT) industry contributes to 3-5% of the world's total carbon footprint (CFP)

- The industry has focused on optimizing power, performance, and area of chips but has neglected environmental impacts

- Embodied CFP has increased over time due to:

- Lower yields in newer technology nodes

- Increased time required for design closure

## **Prior work and our contributions**

- ACT: Architectural carbon modeling tool [Gupta et. al. ISCA 2022]

- Modeled embodied carbon  $\bullet$

- Assumed constant packaging overheads

## **Our key contributions:**

- Proposed heterogenous integration (HI) for sustainability

- Developed a tool for CFP analysis for heterogeneous systems

- Developed CFP models for advanced packaging technologies

- Developed CFP models for design

**Arizona State**

University